### **ADVANCED PROCESSOR PLATFORMS FOR DEVICES**

**Carlo Reita**

Stakeholder Workshop – Smart Networks and Services Partnership, 2 October 2019, Dresden

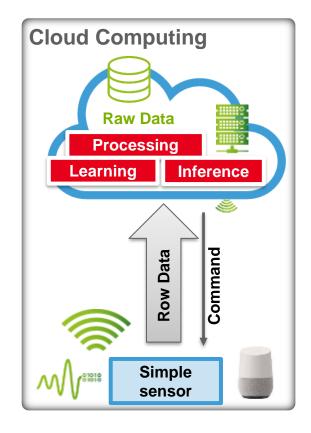

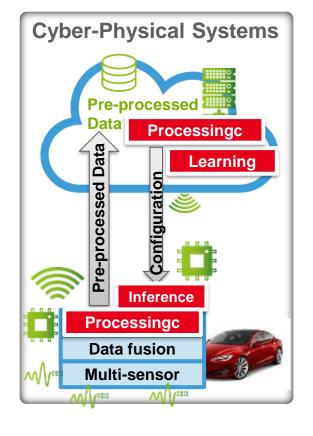

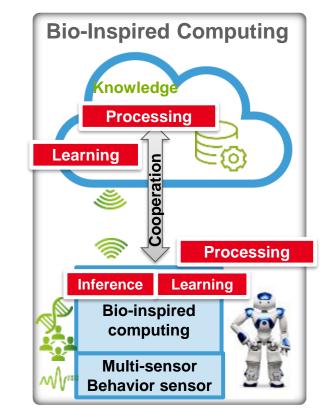

- Evolution of Networks and usages will require more computing all along the communication chain

- Sovereignty and benefits to the citizens at large can be guaranteed only by EU actors strong presence at all levels of the supply and value chains

- New networks and applications can represent the return of EU industry to consumer and infrastructure industry

# **Network distributed computing need specialized hardware**

- Optimize power consumption

- Reduce data transfer

- Reduce latency

- Integrate sensing and processing

- Adaptation to the environment, customization

- Incremental / Online learning

- Design and Programming Software tools

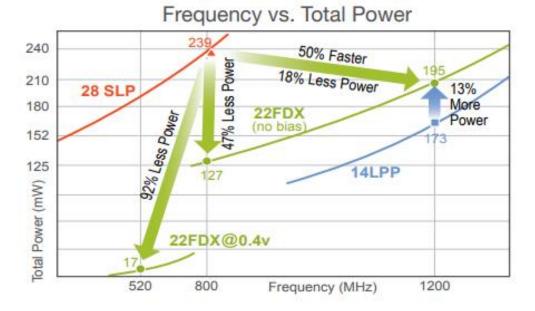

## High Performance and Low Power

#### **IP** Overview

The 22FDX Platform IP portfolio includes a wide range of silicon-proven high performance, power-optimized solutions for a broad set of applications.

|                         |                | Fou                                               | Indation       | IP         |             |  |  |  |  |

|-------------------------|----------------|---------------------------------------------------|----------------|------------|-------------|--|--|--|--|

| Standard C              | ell Low F      | Low Power/Performance/Dense/Low Leakage Libraries |                |            |             |  |  |  |  |

| Memory                  | HP/H           | HP/HD/ULL/TP/DP, SRAM, Register File, ROM         |                |            |             |  |  |  |  |

| GPI0 1.2-1.8V/3.3V, ESD |                |                                                   |                |            |             |  |  |  |  |

| Body Bia                | s Body         | Body Bias Generator, Dynamic Body-bias Controller |                |            |             |  |  |  |  |

|                         |                | Int                                               | terface I      | P          |             |  |  |  |  |

| DDR3/4 LPDE             |                | DR3/4                                             | USB2/3.x       | PCle       | SATA        |  |  |  |  |

|                         |                | )-PHY/<br>PHY                                     | HDMI 2.0       | LVDS       | XAUI        |  |  |  |  |

| Wirel                   | ess Co         | nnectiv                                           | ity IP         | Non-volati | e Memory IP |  |  |  |  |

| BLE                     | WiFi           | NB-loT                                            | Cat-M1         | OTP        | eFuse       |  |  |  |  |

|                         | )              | Analog                                            | IP             |            | Core IP     |  |  |  |  |

| PLL                     | ADC/<br>DAC    | Video<br>DAC                                      | Audio<br>CODEC | LS         | RISC-V      |  |  |  |  |

| RTC                     | Temp<br>Sensor | Process<br>Monitor                                |                | Regulator  |             |  |  |  |  |

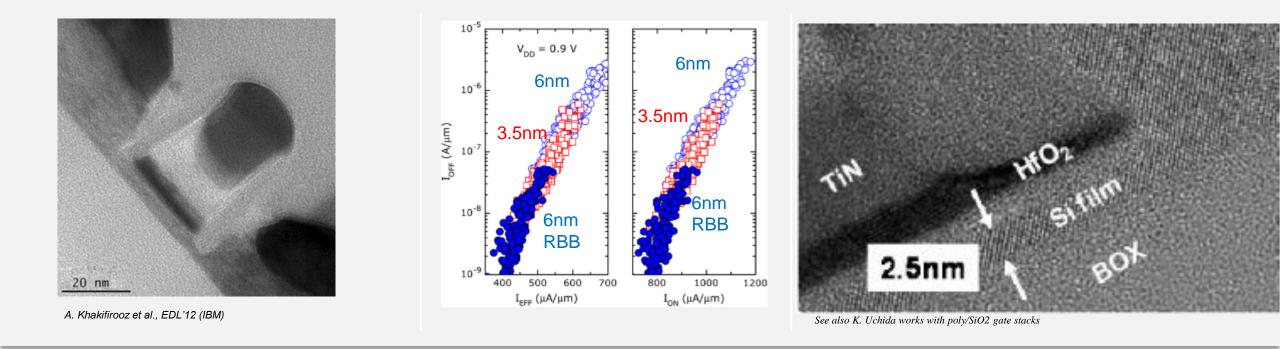

# **FDSOI device scalability: experiments**

- Extremely scaled FDSOI CMOS have already demonstrated

- With excellent device performance

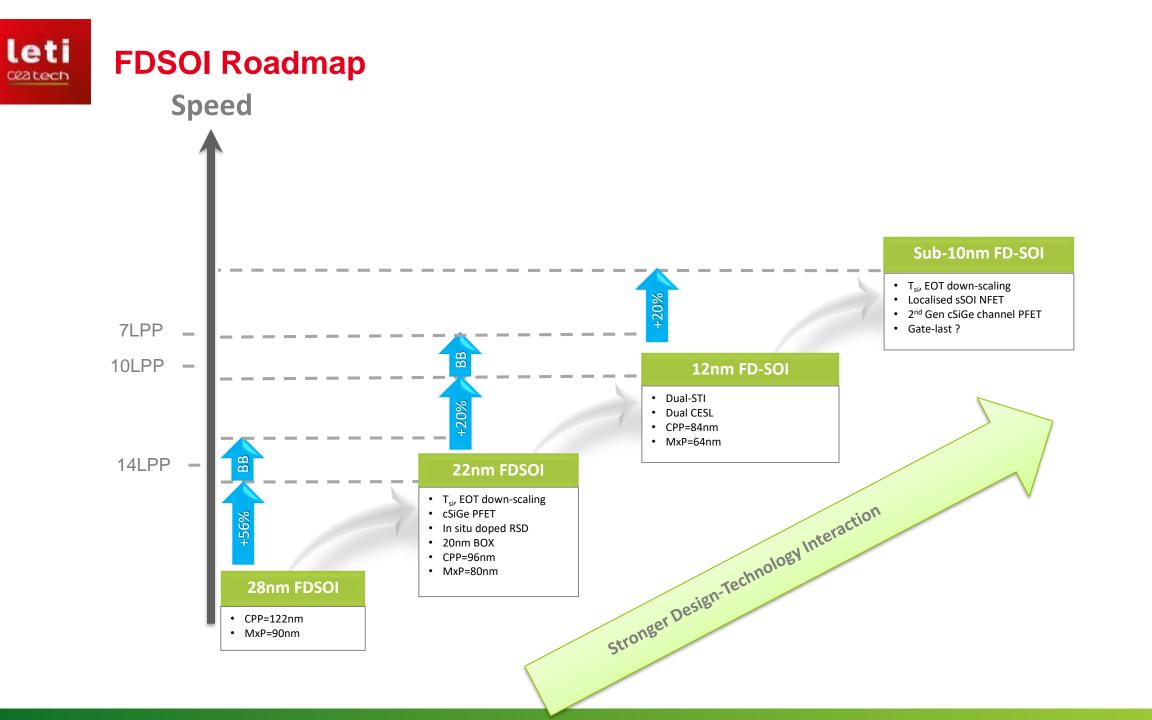

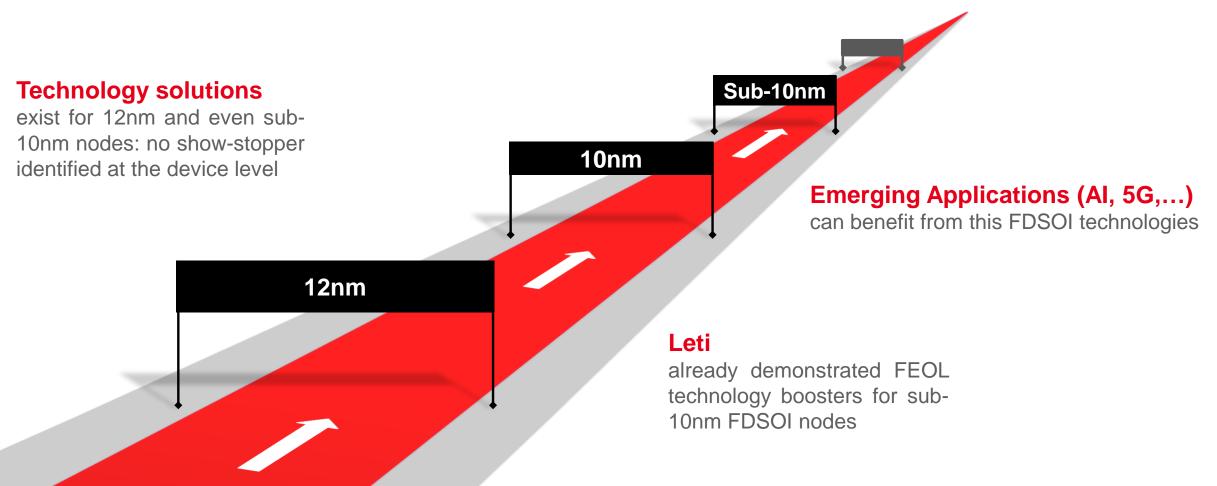

#### leti A roadmap for power efficiency and performance in Europe

ceatech

## And then going up

leti ceatech

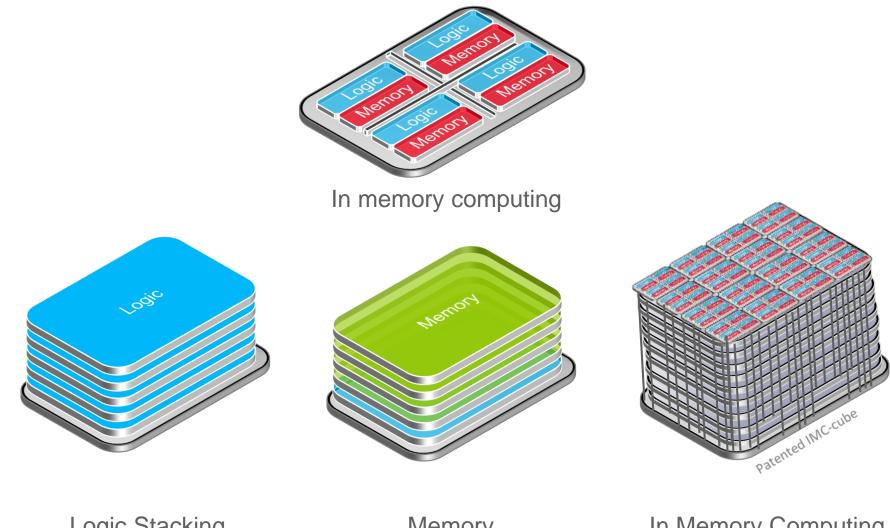

Logic Stacking

Memory Stacking In Memory Computing Stacking

### Leti Industrial environment in EU

- Europe has lost his position in advanced digital design and fabrication

- But this is not irreversible:

- Important competences are still present

- Market and applications evolution (like 5G and 6G) open up new opportunities

- EU citizens demands, regulations and sovereignty need specific EU solutions

### Kalray: High performance multicore

| Quad<br>core | SMC | GP | IOs [ | DDR3 | Quad<br>core |

|--------------|-----|----|-------|------|--------------|

| PCle<br>Gen3 | С   | С  | С     | С    | PCle<br>Gen3 |

| <u> </u>     | С   | С  | С     | С    | L 0          |

| Ethernet     | С   | С  | С     | С    | Ethernet     |

| Eth          | С   | С  | С     | С    | Eth          |

| Quad<br>core | SMC | GP | IOs [ | DDR3 | Quad<br>core |

#### MPPA<sup>®</sup> Bostan with 16 clusters

#### **Core architecture**

#### Compute/System Cores

- 64-bit/32-bit architecture / 600Mhz

- 5-issue VLIW cores

- 8KB instruction cache / 8KB data cache

- IEEE 754-2008 Floating Point Unit (FPU)

- 1 FLOPs (SP) / 0.5 TFLOPs (DP) / 1 TOPs

- Memory Management Unit (MMU)

- ISA with extensions for encryption

- Crypto co-processors (AES, SHA, CRC, etc.)

#### Master cores

- 64-bit/32-bit architecture

- 32KB instruction cache per core

- 32KB data cache shared between 4 cores

- Data cache can be configured as a shared 128KB data cache among 4 SMP Quad cores

- Memory Management Unit (MMU)

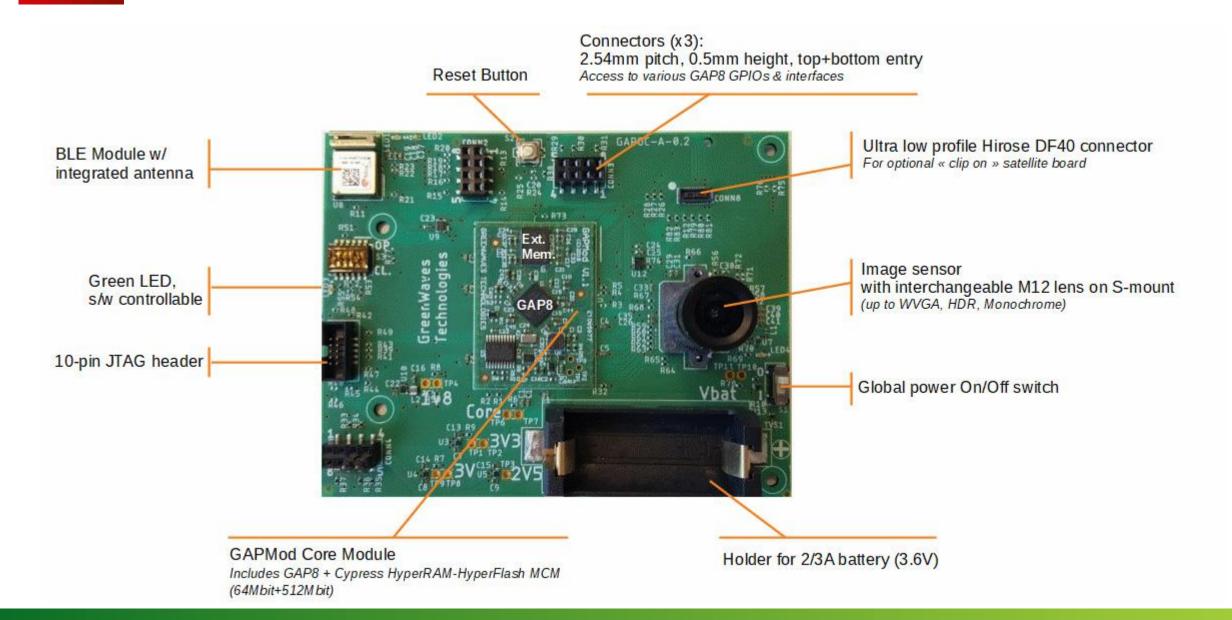

## **Greenwaves: Computer Vision Battery Powered**

leti

ceatech

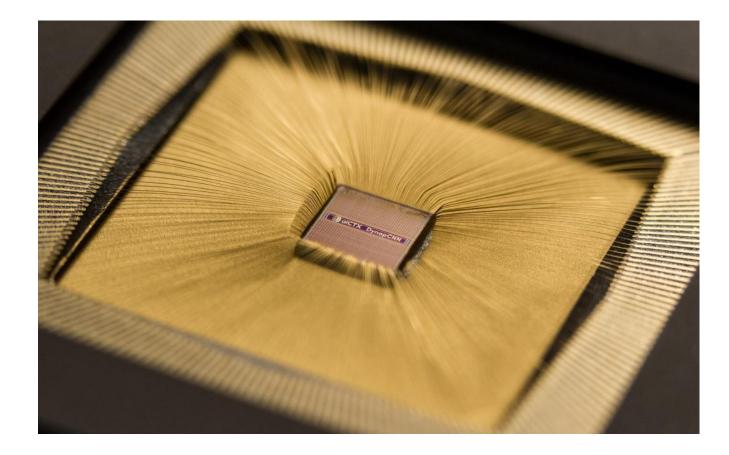

# aiCTX: World's First 1M Neuron, Event-Driven Neuromorphic Al Processor for Vision Processing

- DYNAP-CNN is a 12mm2 chip, fabricated in 22nm FDSOI technology, housing over 1 million spiking neurons and 4 million programmable parameters, with a scalable architecture optimally suited for implementing Convolutional Neural Networks..

- Issued from the H2020 program NeuRAM3

- Higher energy efficiency at same performance than Intel Loihi

### **Leti** Industrial environment in EU

Europe has lost his position in advanced digital design and fabrication

# • But this is not irreversible:

- Support is needed for both the design and technology communities to maintain an healthy ecosystem

- IDMs, foundries and fabless have all a role to play.

leti

Ceatech

|      | Submitt<br>ed | Accepted | % of<br>total | <ul> <li>EU dropped another 22%<br/>in 2019</li> </ul> |

|------|---------------|----------|---------------|--------------------------------------------------------|

| 2015 | 132           | 49       | 24            |                                                        |

| 2016 | 120           | 48       | 23            | (21% drop in 2018)!                                    |

| 2017 | 139           | 39       | 19            | • NA & FE increased 3-5%                               |

| 2018 | 109           | 35       | 17            | (0-1 % in 2018)                                        |

| 2019 | 85            | 30       | 15            |                                                        |

- Digital Systems (4.6%)

- Power Management (8%)

- Europe Research Centers & Universities are suffering (50% reduction last year)

- Need some support to be at the top level

Since 2015, H2020 has been actively investing in the development and the roll-out of 5G. The European Commission invested over **700MEUR** in 5G PPP projects over 3 different phases:

- H2020 Phase 1 (2015): funding projects focusing on performing fundamental research for 5G networks

- => 19 projects

- H2020 Phase 2 (2017): funding projects focusing on proof-of-concepts, experiments, verticals.

- => 21 projects

- H2020 Phase 3 (2018): funding projects on the rollout of a 5G platform and large-scale

& cross-boarder end-to-end trials

- => 16 projects

- Only few projects integrate circuit design activities and none of them Components development

- Phase 3 demonstrator rely on COTS or dedicated products from US & ASIA

leti

Ceatech

- Demonstrator with COTS are lower cost, need less resources is less risky and can be more powerful than silicon demonstrator

- As a conclusion, a project proposal with COTS demonstrator will be far more competitive than a proposal with Silicon based demonstrator

- However, COTS demonstrators DO NOT DEMONSTRATE the suitability of the approach for consumer products

- COTS demonstrators **DO NOT POSITION** Europe for the future markets, no added value

- New European Fabless companies should emerge

• Demonstrator with COTS are lower **cost**, need less **resources** is

Dedicated EU Calls are needed to support Innovative Component Design, Fabrication and Test from R&D groups and Design Houses to stimulate the emergence of new actors

Dedicated schemes to support fabrication of demonstrators in EU are needed to insure access to domestic technologies for the above groups

# Industrial environment in EU

#### **Boosting Electronics Value Chains**

in Europe

A report to Commissioner Gabriel

19 June 2018

SOITEC, STMicroelectronics, X-FAB, Robert Bosch, ASML, Globalfoundries, UMS, Infineon, FhG uEV, CEA-LETI, imec

#### 7. Seizing new opportunities

leti

ceatech

New computing paradigms, such as neuromorphic/quantum computing accelerators and complex integration, present new opportunities for developing the next generation of distributed/edge computing as well as centralised computing for the cloud (HPC) supporting the digital transformation of Europe. *Europe must, therefore, take a leadership role in the development of these technologies.*

- 8 Create a pan-European research infrastructure for advanced computing technologies We are calling for the creation of a pan-European infrastructure for developing, testing, experimenting and innovating in advanced computing technologies, leading to delivery of a digital hardware computing toolbox for European industries. A "moon-shot", mission-driven approach will be needed to achieve this European next-generation computing platform exploiting ultra-low power technologies and neuromorphic/quantum accelerators. This will require:

- the set-up of a joint state-of-the-art technological platform at European RTOs to design, manufacture and test prototype devices of future-generation processors and accelerators in order to prepare for an industrial uptake of these new technologies in European systems houses;

- the commitment of leading European micro-/nanoelectronics RTOs to forge a strategic alliance in close alignment with European semiconductor manufacturers, IDMs and foundries, as well as system houses to reach this goal.

# EU RTOs cooperation for Next Generation Computing (NGC alliance)

# NGC Alliance : key indicators (3 RTOs combined)

9.000 researchers

35.000 m<sup>2</sup> cleanroom

€1.300 million annual budget

180 startups created

3.000 publications each year

Join our ambition !

Leti, technology research institute Commissariat à l'énergie atomique et aux énergies alternatives Minatec Campus | 17 rue des Martyrs | 38054 Grenoble Cedex | France www.leti-cea.com